Faster alignments increase productivity!

At Dharmacon, Inc., we spend a lot of our time aligning sequences, so we are always looking for ways to improve our alignment efficiency. Sequence alignments are essential for making sure our product designs target the correct genomic location or gene transcript with no off-targets. When improving alignment efficiency, most people look to develop faster software aligners by refactoring known algorithms, creating new algorithms, or leveraging parallelization. Alternative to improving the software, researchers can investigate ways to make the underlying hardware more efficient by using newer hardware technologies such as Graphical Processing Units (GPUs) and Field-Programmable Gate Arrays (FPGAs).

Implementing an algorithm using GPUs and FPGAs is now more possible due to the increasing capabilities of this hardware and a reduction in their cost. For example, Amazon Web Services recently announced that they will be providing FPGAs on their EC2 F1 compute instances, so customers can create custom hardware designs for their application.

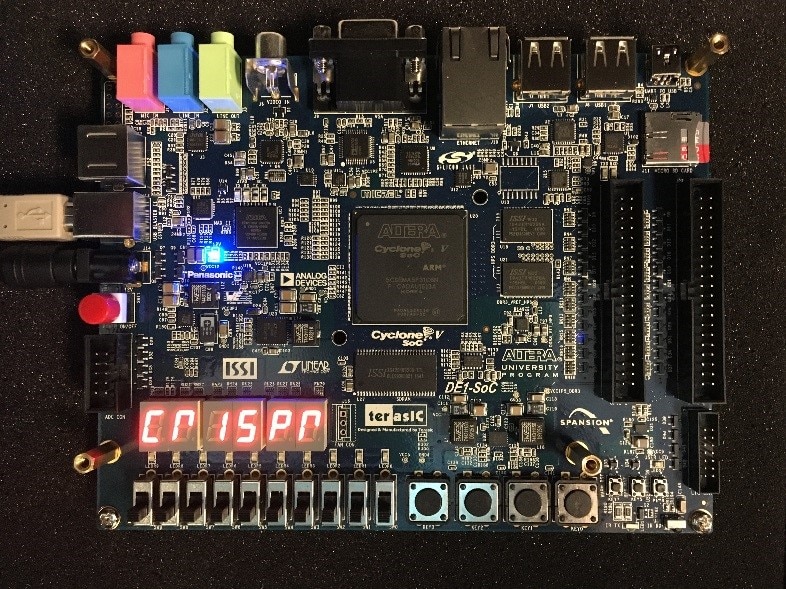

Terasic DE1-SoC Development Board

Accessibility to powerful FPGAs through services like this should provide researchers the motivation to develop novel and more efficient algorithms, such as improving sequence alignment specificity, and several publications have already illustrated that FPGAs can provide dramatic increases in alignment efficiency (2 fold to >100 fold)1–7. Based on these increases, the Dharmacon BioIT team has started to investigate using FPGAs to improve our alignment efficiency. This will allow us to spend more time focusing on our larger scientific goals, which is to design new, high-quality products and novel algorithms that lead to ground-breaking scientific discoveries.

Author: Jesse Stombaugh, Bioinformatics Developer at Dharmacon

References

- Fehér, P., Fülöp, A., Debreczeni, G., Nagy-Egri, M. & Vesztergombi, G. Simple scalable nucleotic FPGA based short read aligner for exhaustive search of substitution errors. Acta Univ. Sapientiae 7, 151 (2015).

- Li, I. T. S., Shum, W. & Truong, K. 160-fold acceleration of the Smith-Waterman algorithm using a field programmable gate array (FPGA). BMC Bioinformatics 8, 185 (2007).

- Olson, C. B. et al. Hardware Acceleration of Short Read Mapping. in 2012 IEEE 20th International Symposium on Field-Programmable Custom Computing Machines 161–168 (2012). doi:10.1109/FCCM.2012.36

- Fernandez, E. B., Villarreal, J., Lonardi, S. & Najjar, W. A. FHAST: FPGA-Based Acceleration of Bowtie in Hardware. IEEE/ACM Trans. Comput. Biol. Bioinforma. 12, 973–981 (2015).

- Kasap, S., Benkrid, K. & Liu, Y. Design and Implementation of an FPGA-based Core for Gapped BLAST Sequence Alignment with the Two-Hit Method . Eng. Lett. 16/3, 443–452 (2008).

- Zhang, P., Tan, G. & Gao, G. R. Implementation of the Smith-Waterman Algorithm on a Reconfigurable Supercomputing Platform. in Proceedings of the 1st International Workshop on High-performance Reconfigurable Computing Technology and Applications: Held in Conjunction with SC07 39–48 (ACM, 2007). doi:10.1145/1328554.1328565

- Waidyasooriya, H. M. uthumala, Hariyama, M. & Kameyama, M. Implementation of a custom hardware-accelerator for short-read mapping using Burrows-Wheeler alignment. Conf. Proc. ... Annu. Int. Conf. IEEE Eng. Med. Biol. Soc. IEEE Eng. Med. Biol. Soc. Annu. Conf. 2013, 651–654 (2013).